## A (Very) Brief History of Computers (I)

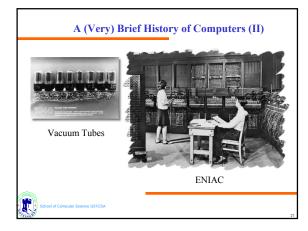

#### The first Generation - Vacuum Tubes (1945 -1955)

### ENIAC (1943 - 1946)

Intended for calculating range tables of aiming artillery Consisted of 18000 tables, 1500 relays, weight 30 tons, consumed 140 KW •Decimal machine •Each digit represented by a ring of 10 vacuum tables. •Designed for artillery range table, but used to perform complex calculations to help determine the feasibility of 14 bomb - general purpose computer •Programmed with multi-position switches and jumper cables.

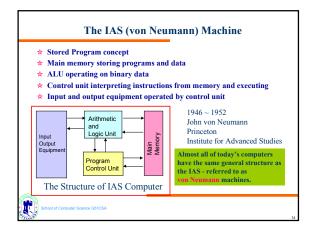

### John von Neumann (1945 -1952) more later ...

Originally a member of the ENIAC development team.

First to use binary arithmetic

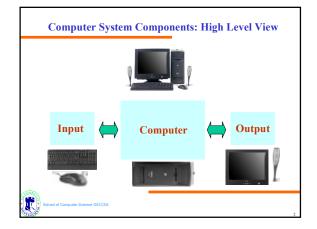

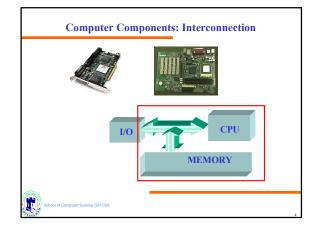

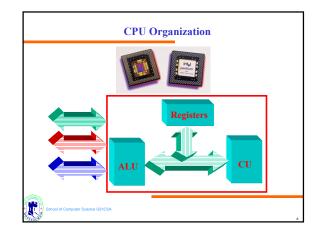

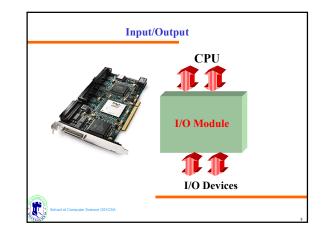

Architecture consists of: Memory, ALU, Program control, Input, Output

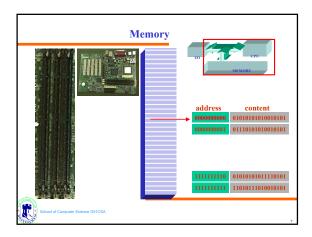

Stored-program concept - main memory store both data and instructions

School of Computer Science G51

ľ

| 1970s Proc                   | 4004                                                    | 8008                           | 8080                                  | 8086                                  | 8088                                                  |

|------------------------------|---------------------------------------------------------|--------------------------------|---------------------------------------|---------------------------------------|-------------------------------------------------------|

| Introduced                   | 11/15/71                                                | 4/1/72                         | 4/1/74                                | 6/8/78                                | 6/1/79                                                |

| Clock<br>Speeds              | 108KHz                                                  | 200KHz                         | 2MHz                                  | 5MHz, 8MHz,<br>10MHz                  | 5MHz, 8MHz                                            |

| Bus Width                    | 4 bits                                                  | 8 bits                         | 8 bits                                | 16 bits                               | 8 bits                                                |

| Number of<br>Transistor<br>s | 2,300<br>(10 microns)                                   | 3,500<br>(10 microns)          | 6,000<br>(6 microns)                  | 29,000<br>(3 microns)                 | 29,000<br>(3 microns)                                 |

| Addressab<br>le Memory       | 640 bytes                                               | 16 KBytes                      | 64 KBytes                             | 1 MB                                  | 1 MB                                                  |

| Virtual<br>Memory            | -                                                       | -                              | -                                     |                                       | -                                                     |

| Brief<br>Descriptio<br>n     | First microcomputer<br>chip, Arithmetic<br>manipulation | Data/character<br>manipulation | 10X the<br>performance of<br>the 8008 | 10X the<br>performance of<br>the 8080 | Identical to 8086 excep<br>for its 8-bit external bus |

| 1980s Processors             |                                        |                                              |                                                                                |                                                        |  |  |  |

|------------------------------|----------------------------------------|----------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------|--|--|--|

|                              | 80286                                  | Intel386™ DX<br>Microprocessor               | Intel386™ SX<br>Microprocessor                                                 | Intel486 <sup>TH</sup><br>DX CPU<br>Microproce<br>ssor |  |  |  |

| Introduced                   | 2/1/82                                 | 10/17/85                                     | 6/16/88                                                                        | 4/10/89                                                |  |  |  |

| Clock<br>Speeds              | 6MHz, 8MHz,<br>10MHz, 12.5MHz          | 16MHz, 20MHz, 25MHz,<br>33MHz                | 16MHz, 20MHz, 25MHz, 33MHz                                                     | 25MHz,<br>33MHz,<br>50MHz                              |  |  |  |

| Bus Width                    | 16 bits                                | 32 bits                                      | 16 bits                                                                        | 32 bits                                                |  |  |  |

| Number of<br>Transistor<br>s | 134,000<br>(1.5 microns)               | 275,000<br>(1 micron)                        | 275,000<br>(1 micron)                                                          | 1.2 million<br>(1 micron)<br>(.8 micron<br>with 50MHz) |  |  |  |

| Addressab<br>le Memory       | 16 megabytes                           | 4 gigabytes                                  | 16 megabytes                                                                   | 4 gigabytes                                            |  |  |  |

| Virtual<br>Memory            | 1 gigabyte                             | 64 terabytes                                 | 64 terabytes                                                                   | 64 terabytes                                           |  |  |  |

| Brief<br>Descriptio<br>n     | 3-6X the<br>performance of the<br>8086 | First X86 chip to handle 32<br>bit data sets | <ul> <li>16-bit address bus enabled low-<br/>cost 32-bit processing</li> </ul> | Level 1 cach<br>on chip                                |  |  |  |

| 1990s Proce              |                                                                                        |                                                                                                                |                                                                          |                                                                                      |  |  |

|--------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|--|

|                          | Intel486 <sup>™</sup> SX<br>Microprocessor                                             | Pentium® Processor                                                                                             | Pentium® Pro<br>Processor                                                | Pentium® II<br>Processor                                                             |  |  |

| Introduced               | 4/22/91                                                                                | 3/22/93                                                                                                        | 11/01/95                                                                 | 5/07/97                                                                              |  |  |

| Clock<br>Speeds          | 16MHz, 20MHz,<br>25MHz, 33MHz                                                          | 60MHz,66MHz                                                                                                    | 150MHz, 166MHz,<br>180MHz, 200MHz                                        | 200MHz, 233MHz,<br>266MHz, 300MHz                                                    |  |  |

| Bus Width                | 32 bits                                                                                | 64 bits                                                                                                        | 64 bits                                                                  | 64 bits                                                                              |  |  |

| Number of<br>Transistors | 1.185 million<br>(1 micron)                                                            | 3.1 million<br>(.8 micron)                                                                                     | 5.5 million<br>(0.35 micron)                                             | 7.5 million<br>(0.35 micron)                                                         |  |  |

| Addressable<br>Memory    | 4 gigabytes                                                                            | 4 gigabytes                                                                                                    | 64 gigabytes                                                             | 64 gigabytes                                                                         |  |  |

| Virtual<br>Memory        | 64 terabytes                                                                           | 64 terabytes                                                                                                   | 64 terabytes                                                             | 64 terabytes                                                                         |  |  |

| Brief<br>Description     | Identical in design to<br>Intel486 <sup>TM</sup> DX but<br>without math<br>coprocessor | Superscalar architecture<br>brought 5X the performance of<br>the 33-MHz Intel486 <sup>TM</sup> DX<br>processor | Dynamic execution<br>architecture drives<br>high-performing<br>processor | Dual independent<br>bus, dynamic<br>execution, Intel<br>MMX <sup>TM</sup> technology |  |  |

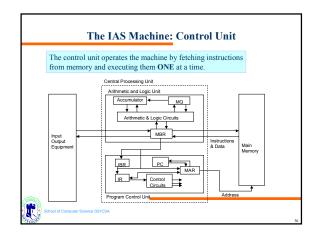

# The IAS Machine: Instruction Cycle

The IAS operates by repetitively performing an *instruction cycle*.

Two sub-cycles:

- During the *fetch cycle*, the opcode of the NEXT instruction is loaded in to the IR and the address portion is loaded into the MAR

- Once the opcode is in the IR, the *execute cycle* is performed. Control circuitry interprets the opcode and executes the instruction by sending out appropriate control signals to cause data to be moved or an operation to be performed by the ALU.

School of Computer Science

ľ